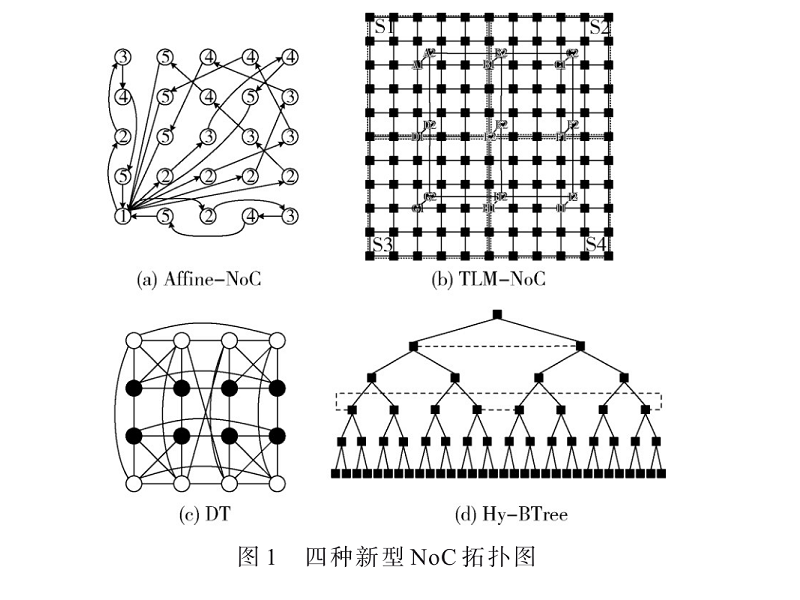

探索分布式仿真方法加速Chiplet系统级验证[EDA与制造][工业自动化]

發(fā)表于:2025/8/14 下午1:44:00

XR芯片系统的EMU全场景AVIP快速迭代验证方案[EDA与制造][工业自动化]

發(fā)表于:2025/8/14 下午1:35:00

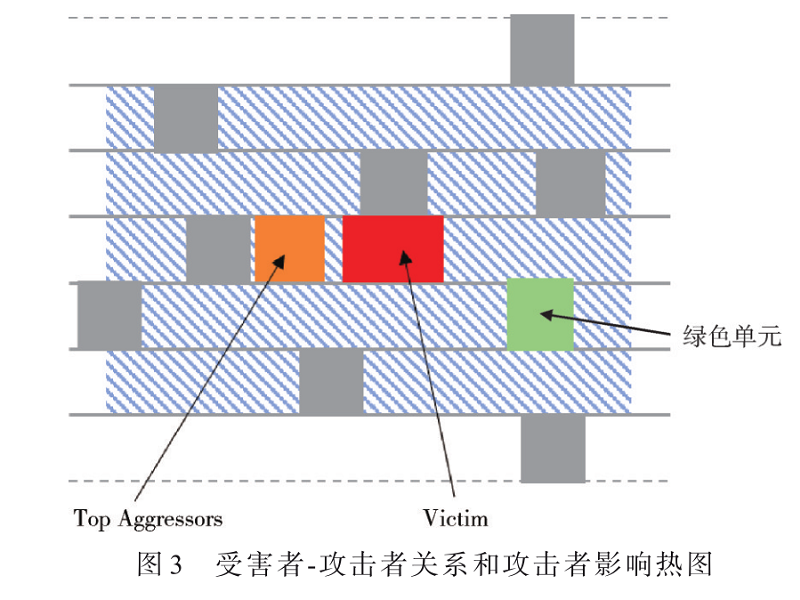

基于Cadence软件平台的分布式电源噪声仿真方法研究[EDA与制造][工业自动化]

發(fā)表于:2025/8/14 下午1:26:00

基于Innovus COD的高效时钟树综合方法及应用[EDA与制造][工业自动化]

發(fā)表于:2025/8/14 下午1:16:00

Voltus Insight AI 在高性能CPU核物理实现上的全流程应用[EDA与制造][工业自动化]

發(fā)表于:2025/8/13 下午5:17:00

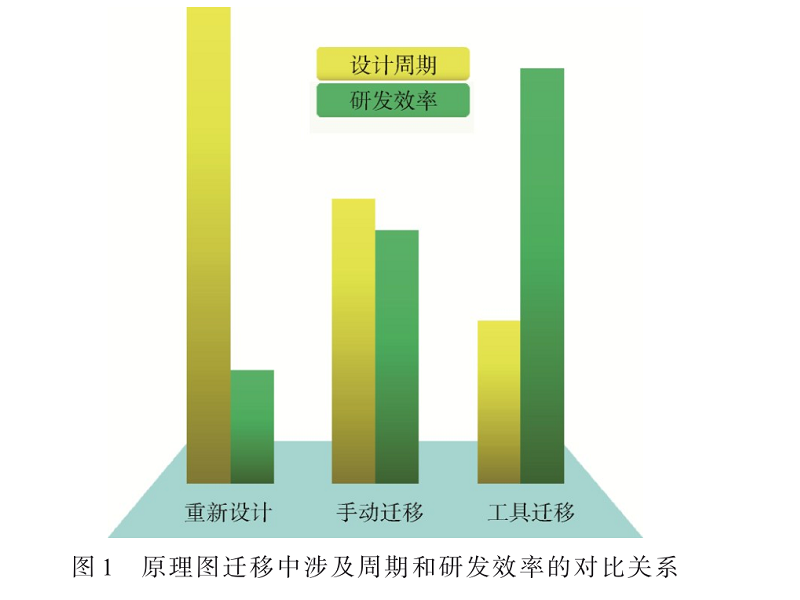

Virtuoso Schematic Migration在模拟电路迁移中的应用[EDA与制造][工业自动化]

發(fā)表于:2025/8/13 下午5:09:00

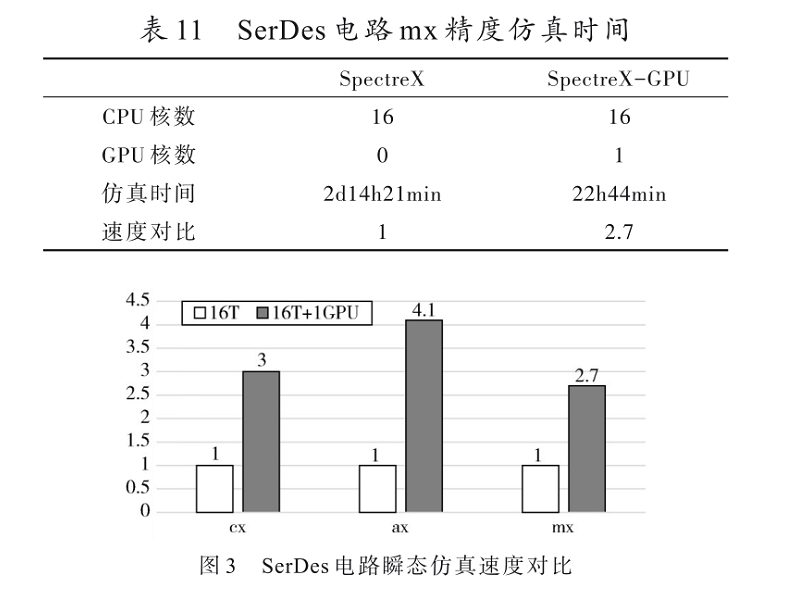

使用SpectreX-GPU加速大规模高精度模拟电路的仿真验证[EDA与制造][工业自动化]

發(fā)表于:2025/8/13 下午5:00:00

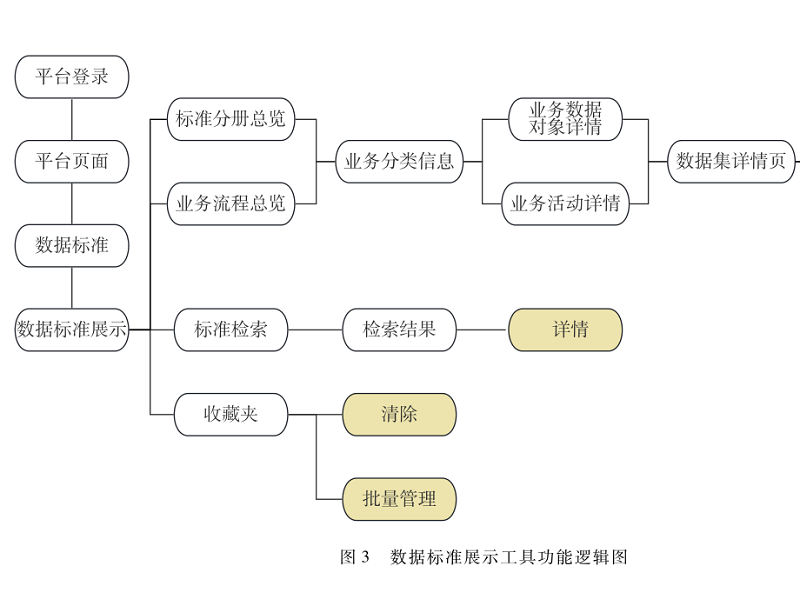

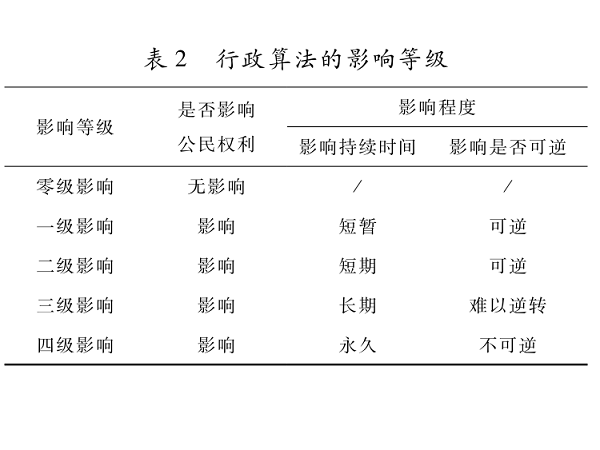

勘探开发数据标准展示工具的设计与实现[其他][其他]

發(fā)表于:2025/7/29 下午4:33:51